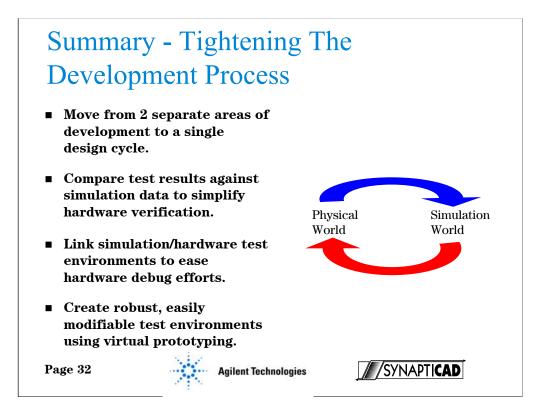

Designers are looking for new tools that will reduce design time and eliminate multiple hardware prototypes. In many ways EDA tools appear to be the answer.

Unfortunately, many projects are delayed when simulation alone fails to create the perfect design. The problem is not in the EDA tools but in the unpredictability of the physical world. Simulation to the exclusion of physical measurements is as inefficient as the traditional design – debug – redesign loop. Today's design teams need tools that work together. This paper demonstrates how EDA tools and physical measurement tools can work together to reduce the design time of your product.

• Demonstrate how EDA tools and traditional test and measurement tools can synergistically work together to reduce the time for design and debug by effectively combining the worlds of simulation and physical measurement.

Page 2

••• Agilent Technologies

/SYNAPTICAD

If you have been reading some technical publications you would start to believe that the world of EDA tools and the world of traditional debug are mutually exclusive.

To some extent this has been true. But it doesn't need to be. In fact today's objective is to look at ways of combining the strengths of both methodologies into a single strategy that will reduce the design cycle, make more efficient use of your time and get a higher quality product to market sooner.

Hardware test and verification is a costly and time-consuming part of the development of digital hardware. Virtual prototyping techniques using a combination of pattern generators, logic analyzers, and EDA software can leverage the work done during the design phase of the product, simplifying the development of a test environment that provides good test coverage and excellent debug capability.

In this paper we will examine problems that have limited the use of virtual prototyping and explore simple, easy-to-use methods for overcoming these problems. We will further demonstrate additional benefits that result when virtual prototyping techniques are combined with the analysis and troubleshooting capabilities of a simulation environment.

This presentation will last 1 hour.

Thank you Gregg. My name is Peter Menegay, and I'm an engineer with Synapticad. If you could turn now to slide 5, I'd like to discuss some of the common problems that have traditionally plagued engineers doing hardware test and verification. I'm sure many of you are familiar with these points, but I'd like to do this in order to provide a launch pad for discussing our proposal for solving these problems, or at least ameliorating them, which is built around this idea that Gregg mentioned of virtual prototyping.

These problems generally boil down to, first of all,

(1) The need to test a subsystem before a complete version of the system is available.

(2) Detecting intermittent errors due to timing problems that don't necessarily manifest themselves during a given test run. This happens when timing violations exist within the circuit but they are not manifesting themselves because of some "favorable" condition, such as temperature, or voltage variation which suppresses the error. Hence the circuit seems to work correctly during the test, but is really hiding a timing violation which could come out later. We would, obviously, like to know about these kinds of violations.

(3) Difficulty with debugging because the test environment doesn't have access to all internal circuit nodes.

(4) Test systems that often don't have the capability to isolate a fault to a single subsystem.

(5) The tedious setup of the hardware test environment (signal names, clock speeds, etc.) because design-level information can't be directly imported from EDA tools. This typically involves an engineer sitting in front of a pattern generator and laboriously programming it, and then sitting in front of a logic analyzer and visually trying to figure out, by looking at the waveforms, whether the circuit is behaving properly. Needless to say, this is a tough assignment, and one which is fraught with error.

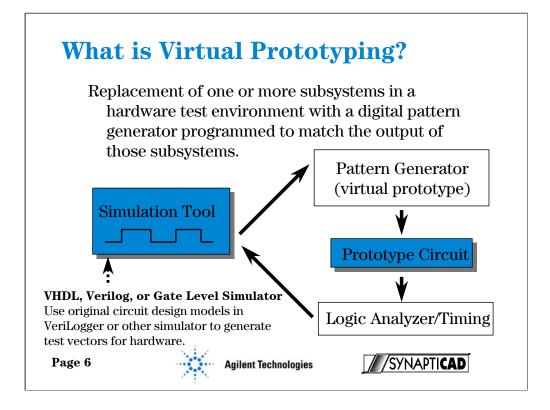

If you'll turn to the next slide, slide 6,

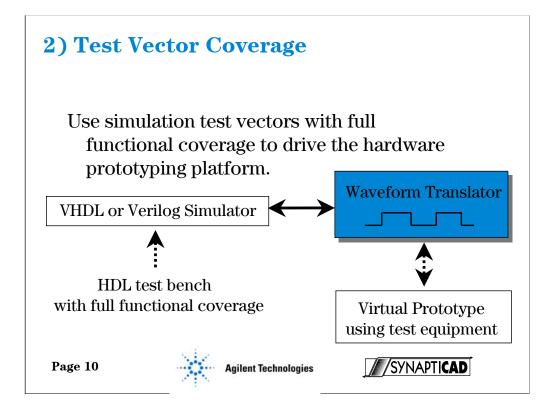

Let's talk about what we mean by virtual prototyping. Virtual prototyping means the combination of the traditional test methods using a pattern generator/logic analyzer with a software simulation tool. The traditional method consists of programming the pattern generator with test vectors for input to the prototype circuit, and then analyzing the response of the circuit by importing it into a logic analyzer. The EDA enhanced method is to use a simulation tool to generate the test vectors, export them to the pattern generator, perform the test on the prototype, and then import the response signals from the logic analyzer back into the same simulation tool. We are going to see that the use of this software environment significantly enhances the test process by reducing the time required to perform the work, and by increasing the quality and reliability of the results.

It is important to note here that the simulation tool is capable of generating stimulus based on a VHDL or Verilog simulation, either done internally or imported from a third party simulator. Also, this tool is capable of taking VHDL or Verilog testbenches and turn them into pattern generator stimulus. Combining this with the ability to read the output of a logic or timing analyzer provides a very powerful yet easy to use environment for hardware test and debug.

During the development of a complex digital system, individual subsystems often get prototyped at different times. With virtual prototyping techniques, these subsystems can be tested in the absence of other subcomponents using general-purpose programmable pattern generators to emulate the unfinished parts of the system (in other words, the pattern generator serves as a virtual prototype).

## What is the difference between Emulation and Virtual Prototyning?

Virtual prototyping solves many of the problems faced during creation of a robust hardware test environment and provides additional debugging capabilities as well: (1) Since data has already been generated during the design process (in simulation) this data can automatically be used as stimulus/or to check against. (2) subsystems can be tested before the whole system is complete, (3) subsystems can be tested in isolation to narrow down the location of bugs and simplify the scope of the debug effort, (4) virtual prototypes can easily be modified to further debug the subsystem under test in the event that design flaws are found in the virtual prototype or to help study the nature of the problem with the subsystem under test, and (5) the speed performance of a subsystem can easily be characterized by increasing the clock frequency at which the stimulus from the virtual prototype is applied.

Virtual prototyping is not a new idea, of course, as pattern generators were created for just this purpose, but several practical issues have limited the complexity of the systems that could be virtually prototyped. Creating complex stimulus that accurately models the environment surrounding a subsystem and programming the stimulus into the pattern generator have, until recently, been engineering-intensive tasks.

An additional challenge using virtual prototypes has been to verify the response of the hardware being tested. The response of the system being tested has to be verified in any kind of hardware verification procedure whether using virtual prototypes or with a complete system test, but a more thorough verification process should be used with a virtual prototypes since they don't react to the output of the system under test (when tested in a complete system the other subcomponents help provide an indirect degree of test coverage since they often depend on the output of the subsystem under test in order to perform correctly themselves).

## NOTE:

Test coverage means how much of circuit we are able to test. It is applying enough different tests to get the circuit fully checked. So if simulation performed enough tests, then automatically the test coverage is adequate.

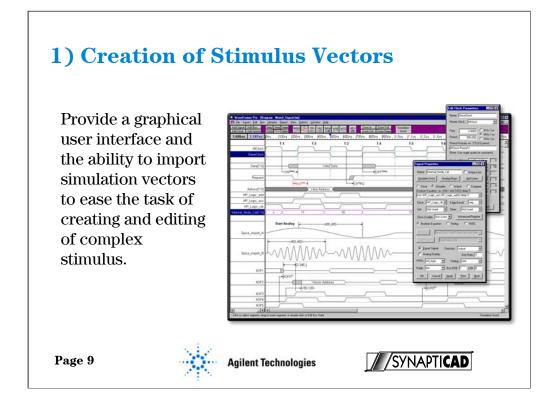

SynaptiCAD's WaveFormer and VeriLogger products offer a timing diagram editing environment that enables stimulus to be created using a combination of graphically drawn signals, timing parameters that constrain edges, clock signals, and temporal and Boolean equations for describing complex, quasi-repetitive signal behavior. Advanced operations on signals such as time scaling and shifting, and block copy and pasting of signal behavior over an interval of time are also supported. This simple, but powerful environment dramatically eases the labor associate with the generation of complex stimulus.

Stimulus can also be created from design simulation waveforms or even from real world data acquired by a logic analyzer. All the above-mentioned manipulations can be performed on these waveforms as well. For example, assume a set of waveform data was gathered from a current generation system running at 50Mhz and the new (not yet completed) system will run at 90Mhz. The captured waveforms can be scaled to the higher speed and then converted to pattern generator stimulus to test the completed portions of the new system.

Reuse complex stimulus vectors developed during simulation verification as hardware stimulus vectors. This ensures that if adequate test vectors were created during simulation verification, you will have adequate functional coverage during hardware verification.

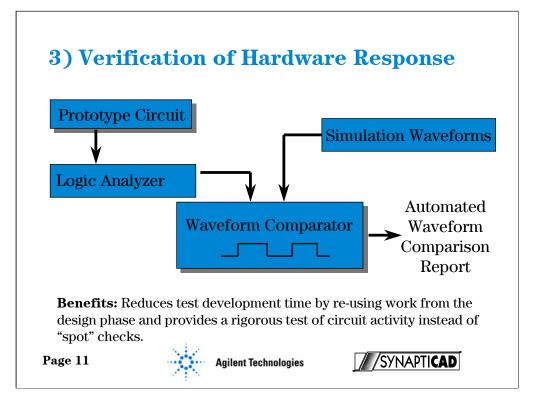

Hardware response verification comprises two basic steps:

1) Capture waveforms from circuit using logic analyzer and import into an automated waveform comparitor.

2) Generate a comparison report against simulation results to verify circuit operation.

There are two kinds of critical comparisons between waveforms: edge-by-edge comparisons and clocked comparisons. An edge-by-edge comparison shows every difference between the compared waveforms and is generally used when comparing asynchronous waveforms or looking for subtle timing errors. Clocked comparisons check for waveform differences slightly before and after clock edges. They are useful for verifying synchronous circuits because they avoid reporting differences that result because of glitches and slight differences in delay times, events which generally don't cause errors in a synchronous circuit.

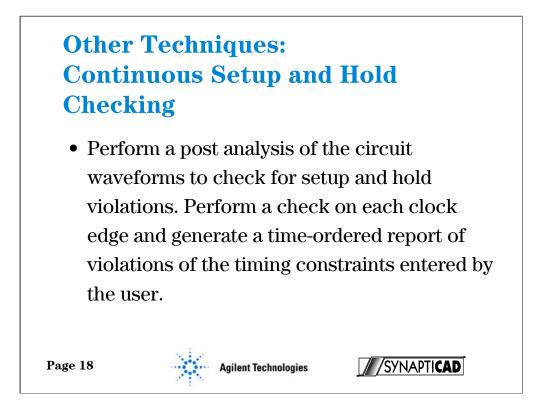

Negative and positive time windows can be specified around the clock edge of a clocked comparison to verify that register and latch timing constraints are being met. This is useful in identifying potential timing errors that generate intermittent errors that may not show up directly during hardware testing. Specifying a negative window time helps to catch setup errors that arise when delay paths through the circuit are too long. Specifying a positive window time helps to catch hold errors that arise when delays paths are too short. These errors often go uncaught in initial system tests because they vary with operating conditions such as temperature and supply voltage. Using time windows to verify stability around the clock edges, potential trouble spots can quickly be identified and investigated.

Negative and positive time windows can be specified around the clock edge of a clocked comparison to verify that register and latch timing constraints are being met.

This is useful in identifying potential timing errors that generate intermittent errors that may not show up directly during hardware testing. Specifying a negative window time helps to catch setup errors that arise when delay paths through the circuit are too long. Specifying a positive window time helps to catch hold errors that arise when delay paths are too short. These errors often go uncaught in initial system tests because they vary with operating conditions such as temperature and supply voltage. Using time windows to verify stability around the clock edges, potential trouble spots can quickly be identified and investigated.

Traditionally, waveform data from a logic analyzer has required visual inspection by an engineer familiar with the operation of the circuit to verify proper operation or to troubleshoot an error. This method is error-prone and time-consuming, especially as the number of waveforms and the amount of data captured increases. Automated comparison guarantees a rigorous check of each data point, ensuring the detection of "small impact" errors that are easily missed during visual inspection of the waveforms.

Another problem with visual inspection of waveforms is that even when an error is spotted, there is no guarantee that the source of the error didn't happen earlier in the waveform data set and was simply missed during visual inspection. This can lead to a slow hunt back in time through the waveform data to the original divergence from correct operation. With automated comparison, the original divergence is immediately detected, speeding the debug process.

Another important advantage of automated verification is it reduces the amount of knowledge required by the verification engineer to test the system. Rarely does even the designer of a system keep a detailed vision of the operation of all the signals in his design (that's the reason for simulators), yet that is exactly the capability needed to spot a hardware error. The simulation environment must "know" exactly how the signals should be acting and "inspect" the waveforms, identify the faulty signal, and display the difference between the actual response and the correct response.

One of the more powerful debug capabilities associated with verifying the hardware results using a simulation environment is the ability to check that the suspected circuit fault would generate the observed results. This can be done by adding the suspected fault to the simulation model, re-running the simulation, and comparing the new simulation results to the captured waveforms. If the waveforms match, the error has most likely been correctly identified. If there are still mismatches further downstream in the waveform data, this is likely an indication that the error has been either misidentified or that the hardware contains multiple errors. Repetition of the above process after identifying each error can reduce the number of times the hardware needs to be changed.

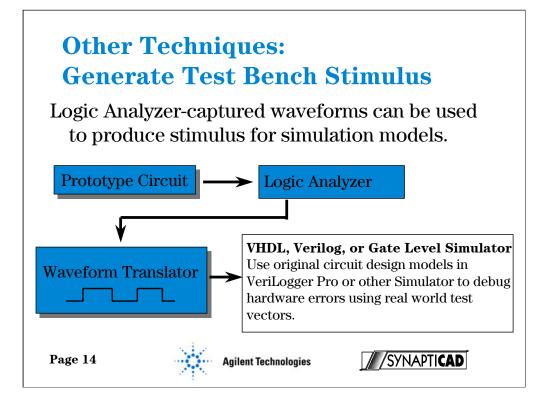

Although this talk has focused on using design data to help verify hardware, the reverse process can also be successfully applied to the design and simulation of new systems. Most systems being designed need to interface with already existing hardware (IC's or entire boards) and simulation models are frequently not available for that hardware. Waveforms from the existing hardware need to be captured with a logic analyzer and converted to HDL test bench code or SPICE stimulus.

Let me give you a quick example of a customer who has used this technique. A customer from Microwave Data Systems was testing an ASIC design in which he needed to generate stimulus. Instead of programming these manually into his VHDL simulator he simply captured output from his upstream components using the simulation software tool(which he had), fed them into a VHDL simulator which he had programmed, and produced the needed stimulus for output to his new design. He reported that the process took about 15 minutes rather than an estimated 2 weeks. This is a real world example from a customer, who without any prompting by us, volunteered this information. Needless to say, these new techniques for testing are going to provide a real productivity boost.

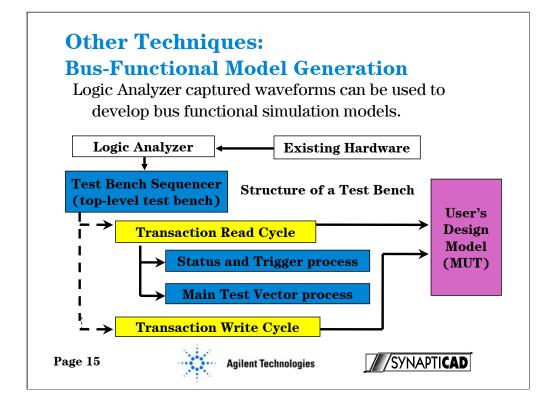

Another feature is the ability to verify that a system being designed can work with an existing piece of hardware. In this case, we use the logic analyzer to capture data from the existing system, where it can be imported into a test bench generation tool where we can massage the waveforms to create a reactive, bus functional model of the existing system. We then use this model to stimulate the simulation model of our new design and to verify it's response. This approach is similar to the technique on the previous slide, but in this case we break up the captured data into reusable "transactions". You can then control the order in which these transactions are applied to your model under test with function calls in the top-level of your test bench. An example of a transaction would be a write cycle or a read cycle by a microprocessor. These transactions can be parameterized in the testbench generation tool by replacing specific data values with variables which can be passed in when you call transaction function call.

When simulating a design using an HDL language, the waveforms should be converted directly to test vectors or used as a starting point by the designer for the creation of a reactive, bus functional model capable of checking and responding to the output of the system being simulated.

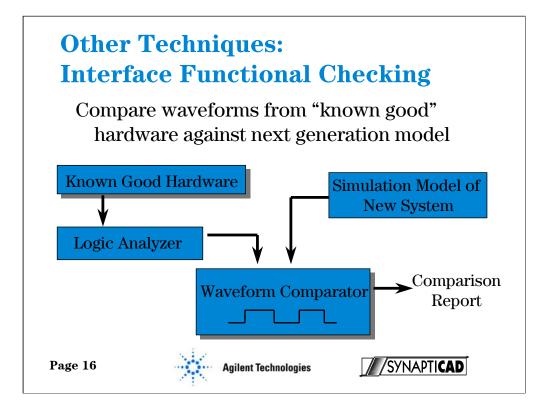

Often the system being designed is the next generation of an existing product with similar functionality. In this case, the new system must generally mimic at least part of the interface of the older system. By performing a waveform comparison between the old system and the new design, correct functioning of the new system can be assured.

| Image: Serie Sector Edit Draw Bus Libraries View Options Window Help       Image: Sector Edit Draw Setus                                         |                                | CONV.TIM - [Diagram] |                  |            |                                  |                                   |                  |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------|------------------|------------|----------------------------------|-----------------------------------|------------------|---------|

| Add Space       Hold       Text                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                | NI CI CI T           |                  |            | Zeemin                           |                                   |                  | _ 5     |

| CommonSig       Reconvergent Fanout Example         SameAsCommon       A) No common delay between D1 and Fan2         SameAsDinput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                |                      |                  |            | C A                              |                                   |                  |         |

| SameAsCommon SameAsDInput Common Comm | 139.3ns <mark>139.3ns</mark> 0 | ps 50ns              | 100ns            | 150ns      | 200ns                            | 250ns                             | 300ns            | 350ns   |

| SameAsCommon SameAsCommon SameAsCommon A) No common delay between D1 and Fan2 A) No common delay between D1 and Fan2 SameAsDinput CommonDelay+ B) CommonDelay is common to Fan1 and Fan2 Common Fan1+ [9.] Setup of 11ns has margin of 9ns Dinput Fan2+ The following delays are the same: CommonDelay = SameDelay = SameDelay, with uncertainity of 10ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | commonSig                      |                      | Recor            | nvergent F | anout Exar                       | nple                              |                  |         |

| SameAsDInput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                | —SameDelay→          |                  | -          |                                  |                                   |                  |         |

| SameAsDInput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SameAsCommon                   |                      | A)               | No commo   | n delay betv                     | veen D1 and                       | l Fan2           |         |

| SameAsDInput CommonDelay+ B) CommonDelay is common to Fan1 and Fan2  Fan1++ [9,] Setup of 11ns has margin of 9ns  Input Fan2+ The following delays are the same: CommonDelay = SameDelay, with uncertainity of 10ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                      | ►+ <10,3         | 30>        |                                  |                                   |                  |         |

| Common Delay+ B) CommonDelay is common to Fan1 and Fan2  Fan1++ [9,] setup of 11ns has margin of 9ns  DInput Fan2+ The following delays are the same: CommonDelay = SameDelay, with uncertainity of 10ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                | L L                  | —D1—++ [-1,]     | S          | etup of 11ns is                  | violated                          |                  |         |

| Common       B) CommonDelay is common to Fan1 and Fan2         B) CommonDelay is common to Fan1 and Fan2         Fan1→→ [9,]         Setup of 11ns has margin of 9ns         Fan2→ Fan2→ CommonDelay = SameDelay, with uncertainity of 10ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SameAsDInput                   |                      |                  |            |                                  |                                   |                  |         |

| Image: Common intermediate     Image: Common intermediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                | _CommonDelay→        | D                |            | N-1                              |                                   |                  |         |

| DInput<br>Fan1→→→[9,] setup of 11ns has margin of 9ns<br>Fan2→→ The following delays are the same:<br>CommonDelay = SameDelay, with uncertainity of 10ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Common                         |                      | В)               |            | Jelay is com                     | mon to Fan                        | and Fanz         |         |

| DInput<br>Fan2 + The following delays are the same:<br>CommonDelay = SameDelay, with uncertainity of 10ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |                      | <b>► +</b> <20,2 | 20>        |                                  |                                   |                  |         |

| Fan2→ The following delays are the same:<br>CommonDelay = SameDelay, with uncertainity of 10ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                | -                    | -Fan1-++ + [9,]  | S          | etup of 11ns ha                  | as margin of 9r                   | IS               |         |

| CommonDelay'= SameDelay, with uncertainity of 10ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Dinput                         |                      |                  |            |                                  |                                   |                  |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                | L                    | Fan2 +           | The        | following delay<br>CommonDelay = | s are the same:<br>- SameDelay, w | ith uncertainity | of 10ns |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DClock                         |                      |                  |            |                                  |                                   | ,                |         |

It is important to document circuit operation by converting captured waveform data into true timing diagrams. The user can add delay, setup, and hold timing parameters to document the temporal relationships between signal transitions. Finally, improvements to the readability of timing diagrams can be obtained by adding text and grid lines. When the timing diagram is complete, WaveFormer Pro can create publication quality WMF, MIF or EPS images for use in Word, FrameMaker or PDF files.

The simulation environment should be able to generate a report of ALL setup and hold timing violations specified between any two signals in a timing diagram regardless of whether the signal is a captured waveform or a simulated waveform (logic analyzers typically only flag the first violation).

Setup and hold time violations in ASICs and PLDs are particularly troublesome because timing violations usually occur on flip-flop inputs that are not directly available at device pins, but are instead a logical function of the device's inputs. Using conventional debugging techniques, these timing violations are extremely difficult to catch because they cannot be directly measured. WaveFormer's ability to simulate internal signals makes it simple to detect timing violations between signals buried inside a chip.

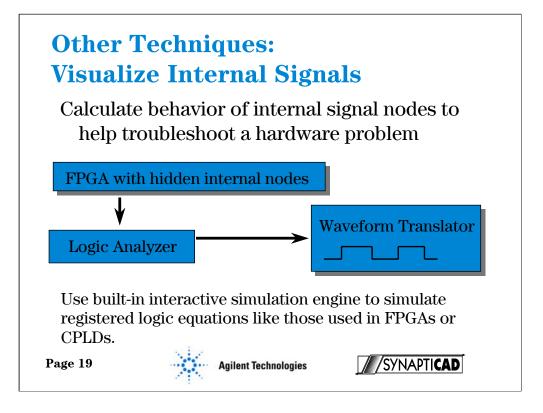

One of the most frustrating problems encountered when debugging a circuit is the inability to see what is happening on all the internal signal nodes of an FPGA or ASIC. A logic analyzer can only show the activity on signals that are brought out on device pins. Unfortunately, many designs are I/O limited. Even when there are no limitations, there are almost never enough pins available to bring out all the useful nodes.

To combat this problem, use a built-in interactive simulation engine that can simulate registered logic equations like those used in FPGAs or CPLDs. By combining this capability with data captured by a logic analyzer, users can determine what is happening not only at the pins of their devices, but also on the internal nodes that cannot be directly probed. This dramatically simplifies the debug process by allowing a designer to effectively trace into a chip to locate the source of the problem.

If you'll turn now to slide 20, this concludes this part of the presentation where I've detailed some of the problems with hardware test and verification and proposed a solution based on the combination of EDA software and the traditional methods. I'd like to emphasize that what we've done here is replaced a difficult to modify hardware test environment with an easy to modify software environment, without sacrificing the "realness", if you will, of hardware testing. Now I'd like to turn it back over to Gregg who's going to provide us with a case study so you can see an example of how these ideas I've been talking about really work.

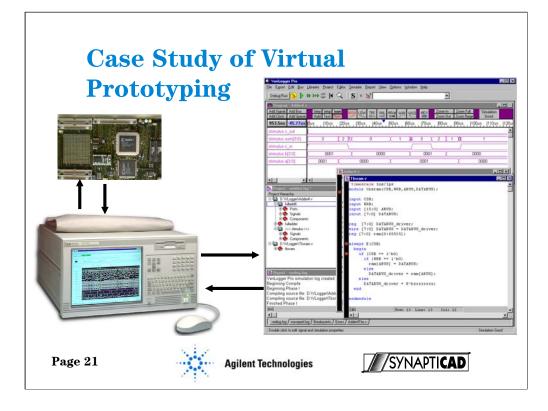

To better understand the processes described in this paper the following case study is provided.

A circuit design will be developed using SynaptiCAD and Xilinx design tools. The design will then be downloaded onto an Associated Professional Systems X240 development board. This board uses a Spartan XS30 FPGA and 256K of SRAM. An Agilent Technologies 16522A pattern generator will provide stimulus to the device under test and the results will be measured with an Agilent Technologies 16717A timing analyzer. The results will then be uploaded to the SynaptiCAD simulator and the results will be automatically compared.

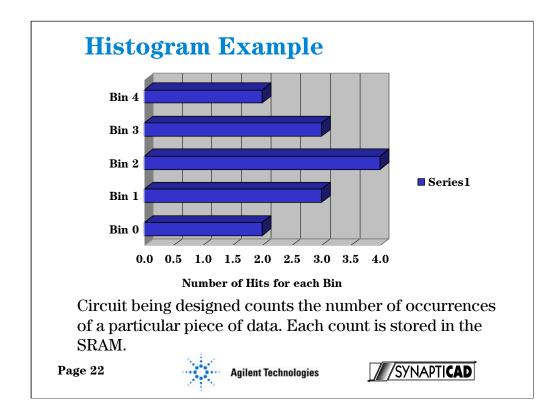

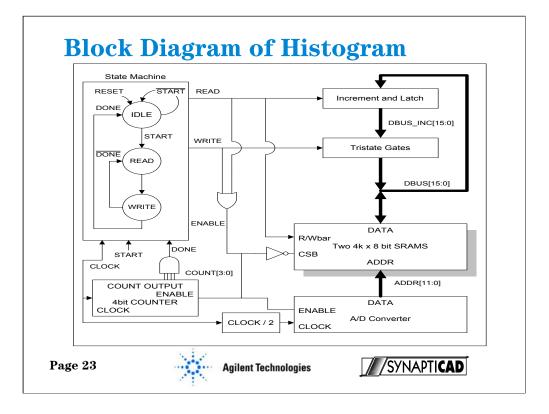

As an example application of the use of a virtual prototype, we will examine the design and debug of a histogram circuit that is used for A/C performance testing of analog-to-digital converters. The histogram circuit counts the occurrences of 12-bit values received from the Analog to Digital Converter (ADC). These "bin" counts can be graphed on a bar chart to show the relative frequency of occurrence of each data value (a histogram chart).

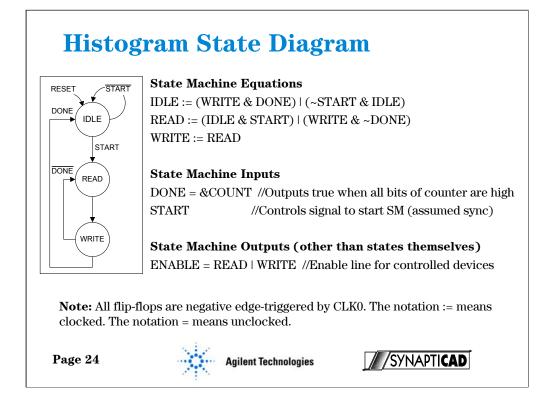

The histogram circuit is composed of three subsystems: the ADC which generates the data to be histogrammed, the data path circuit that stores and increments the bin count for each value, and the state machine that generates the control signals for the data path circuit.

In this design the ADC will not be created. Instead the Agilent Technologies pattern generator will provide test vectors to simulate the 12 bit output. The purpose in not creating the ADC is to demonstrate that when part of a design is not available it is still possible to test and debug the design. This not only saves time, but by testing smaller pieces it becomes easier to find problems when they do occur.

The equations that describe the circuit were converted to a Verilog model of the circuit for verification inside VeriLogger's simulation environment.

WaveFormer and VeriLogger can import simulation waveforms from other simulation environments, so the next several steps could also be performed using a third party simulator which can export to a waveform format such as Value Change Dump (VCD files).

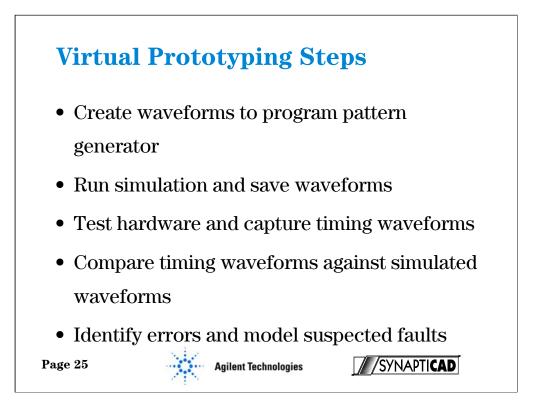

For this case study we followed these basic steps to find out if the design would perform as expected.

• We used the timing diagram editor in VeriLogger Pro to create the ADC waveforms for the input to the physical circuit

•We ran the simulation and verified that the design worked.

•Next the timing waveforms were converted to patterns for the pattern generator.

•Now the pattern generator provides input to the histogram circuit on the FPGA and the Agilent timing analyzer captures the data.

• The real timing behavior of the design is loaded into the SynaptiCAD Verilogger Pro and a comparison is made between the simulation and the real-world results. The tool automatically makes the comparisons and identifies differences.

•Let's take a look at each step

| Add Clock Add Space   | Delay         Setup         Sample         HIGH         LÓW         TRI         VAL         INVal         WHI         MCD         HEX         Zoom In         Zoom Full         Simulate           r         Hold         Text         Marker         LÓW         TRI         VAL         INVal         WHI         MCD         HEX         Zoom Out         Zoom Range         Diagram |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.932us 1.738us       | Ons 200ns 400ns 600ns 800ns 11.0us 11.2us 11.4us 11.6us 11.8us 2.0us                                                                                                                                                                                                                                                                                                                    |

| CLKD                  |                                                                                                                                                                                                                                                                                                                                                                                         |

| ADDR[7:0]             | 00                                                                                                                                                                                                                                                                                                                                                                                      |

| DBUS_PAT[7:0]         |                                                                                                                                                                                                                                                                                                                                                                                         |

| CSB_PAT               |                                                                                                                                                                                                                                                                                                                                                                                         |

| WRITEB_PAT            |                                                                                                                                                                                                                                                                                                                                                                                         |

| OEB_PAT               |                                                                                                                                                                                                                                                                                                                                                                                         |

| FPGA_ENABLED          |                                                                                                                                                                                                                                                                                                                                                                                         |

| INJECT_FAULT          |                                                                                                                                                                                                                                                                                                                                                                                         |

| reset                 |                                                                                                                                                                                                                                                                                                                                                                                         |

| START                 |                                                                                                                                                                                                                                                                                                                                                                                         |

| CSB                   |                                                                                                                                                                                                                                                                                                                                                                                         |

|                       |                                                                                                                                                                                                                                                                                                                                                                                         |

| WINTE                 | te waveforms to program pattern generator                                                                                                                                                                                                                                                                                                                                               |

| DONE                  | te waveforms to program pattern generator                                                                                                                                                                                                                                                                                                                                               |

| DONE                  | te waveforms to program pattern generator                                                                                                                                                                                                                                                                                                                                               |

| DONE<br>WRITEB<br>OEB |                                                                                                                                                                                                                                                                                                                                                                                         |

| DONE                  | te waveforms to program pattern generator         FF       0       1       FF[0]       1       FF[1]       2       FF[2]       3       FF[2]       3       1                                                                                                                                                                                                                            |

| DONE<br>WRITEB<br>OEB |                                                                                                                                                                                                                                                                                                                                                                                         |

| DONE<br>WRITEB<br>OEB |                                                                                                                                                                                                                                                                                                                                                                                         |

• In VeriLogger Pro, load the project containing the simulation models and test benches.

• Click on the "Build Active project" icon and then click the "Run Simulation" icon. VeriLogger Pro will take the Verilog design files and simulate the design.

• Use the "Export" menu functions to export the simulation waveforms to a file that can be read by the Agilent Technologies Pattern Generator.

| Naviga                                                                                                                                                                                                                                                                                                                                                                                                     | ~                                    |                                                                                                  |                                                                            |                                                                         |                                                                              |                                                                    |                                                                         |                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                            | Sequence                             | Mac                                                                                              | ro                                                                         | D-+-+-                                                                  | T-381                                                                        | - D                                                                |                                                                         |                                                                                                                                                                                                               |

| Line                                                                                                                                                                                                                                                                                                                                                                                                       | Instruction                          | ADDR<br>Hex                                                                                      | DBUS_F<br>Hex                                                              | PAT CSB_PA                                                              | T WRITEB_PAT                                                                 | OEB_PAT                                                            | FPGA_EN                                                                 | IABLED INJECT_FAULT F                                                                                                                                                                                         |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>2<br>3<br>4<br>5<br>6<br>7<br>11<br>2<br>3<br>4<br>5<br>6<br>7<br>11<br>2<br>3<br>4<br>5<br>6<br>7<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10 | INIT START<br>INIT END<br>MAIN START | <br>00<br>00<br>02<br>02<br>04<br>04<br>00<br>00<br>02<br>02<br>02<br>04<br>04<br>00<br>00<br>00 | 00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00 | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | Add Signal         Add Bus         Dr           Add Clock         Add Spacer         H           1.932us         1.738us         Drs           CLK0         CLK0         //////////////////////////////////// |

| Jse v                                                                                                                                                                                                                                                                                                                                                                                                      | vavefor                              | ms                                                                                               | to p                                                                       | rogran                                                                  | n patter                                                                     | n gen                                                              | erato                                                                   | reset                                                                                                                                                                                                         |

• Transfer the stimulus file to the pattern generator. Note, that the signal names in the pattern generator automatically match those in the simulator.

• The file was transferred over the Lan. It's interesting to note that the logic analyzer can mount the C drive on the PC as its disk drive so the analyzer can just load the file from the C drive. This saves having to even to a file transfer.

| File Edit Options | Hel                                                          |

|-------------------|--------------------------------------------------------------|

| Navigate Run      |                                                              |

| Search Goto Ma    | arkers Comments Analysis Mixed Signal                        |

|                   | ₹=0 Time t from Trigger t =-67.775 us                        |

|                   |                                                              |

| G2: CSB           | <b>∃</b> = 0 Time <b>↓</b> from Trigger <b>↓</b> = 85.166 us |

| Seconds/div 🗖     | 50.000 us 📓 Delay [118.499 us 🖗                              |

|                   | G1 tr G2                                                     |

| CSB all 1         | 0                                                            |

| IDLE all 1        | 0                                                            |

| READ all 0        |                                                              |

| WRITE all         |                                                              |

| DONE all          | 0                                                            |

| WRITEB all        |                                                              |

| OEB all           |                                                              |

|                   | FF 00 01 FF 00 FF 01 FF 01 02 FF 01                          |

| START_B15 all     |                                                              |

|                   |                                                              |

|                   | Dup and conture timing would farm output                     |

|                   | Run and capture timing waveform output                       |

| 4                 |                                                              |

|                   | and 100                                                      |

| Page 28           | Agilent Technologies                                         |

• Run the pattern generator to provide stimulus to the Xilinx Spartan XCS30 FPGA. The pattern generator is simulating a missing ADC and the missing control logic circuit.

• Use the timing analyzer in the logic analyzer to capture the output data of the histogram circuit.

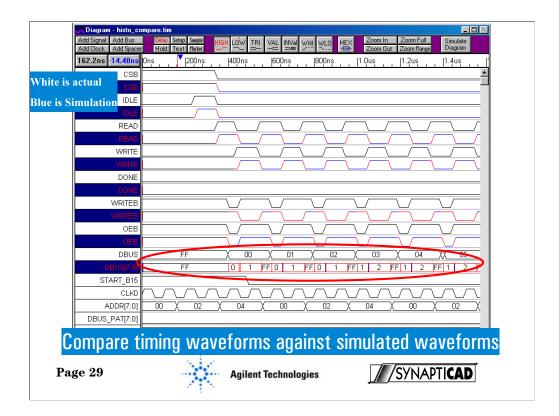

• Use file compare in VeriLogger. This tool will interleave the simulation waveforms with the actual waveforms and then highlight in red any waveform areas that don't match.

• We can quickly see that simulation and real-time measurements don't match. There is a problem.

| Histgoo<br>Add Signal Add Bus       |                                                                                  |

|-------------------------------------|----------------------------------------------------------------------------------|

| Add Clock Add Space 808.3ns 631.7ns | r Hold Text Marker — — — — — — — — — — Kara Marker — Zoom Out Zoom Range Diagram |

| CSB                                 |                                                                                  |

| CSB                                 |                                                                                  |

| IDLE                                |                                                                                  |

| IDLE                                |                                                                                  |

| READ                                |                                                                                  |

| READ                                |                                                                                  |

| WRITE                               |                                                                                  |

| WRITE                               |                                                                                  |

| DONE                                |                                                                                  |

| DONE                                |                                                                                  |

| WRITEB                              |                                                                                  |

| OEB                                 |                                                                                  |

| OEB                                 |                                                                                  |

| DBUS                                | FF X00X 01 X00X 01 X00X 01 X 02 X01X 02 X04X 02                                  |